Intel officially revealed the first architectural details related to Tremont at Linley Fall Processor Conference. It is Intel’s latest and most advanced low-power x86 CPU architecture to date. According to Intel – ‘Tremont offers a significant performance boost over previous generations.’

Intel Tremont Chief Architect, Stephen Robinson, states – ‘Tremont is Intel’s most advanced low-power x86 architecture to date. We focused on a range of modern, complex workloads while considering networking, client, browser, and battery so that we could raise performance efficiently across the board. It is a world-class CPU architecture designed for enhanced processing power in compact, low-power packages.’

Why It Matters | Tremont

Intel states that the new microarchitecture brings noticeable IPC gains when compared to previous generations of Intel’s low-power CPUs. The new platform is for enhanced processing power in a compact, low-power form-factor. As such, the platform will enable a new generation of innovative form factors. Such as for creative applications, IoT, client devices, and more.

And combining this with Intel’s broader IP portfolio enables a new generation of products. The microarchitecture makes use of Intel Foveros, which is Intel’s 3D packaging technology. Tremont is integrated into a wider set of silicon IPs in Lakefield, which is slated to power breakthrough innovative devices such as the recently announced Microsoft Surface Neo.

Performing architectures are the core of chips that collect and process data. Low-power solutions are important to enable new use cases powered by smaller form factors.

The Details

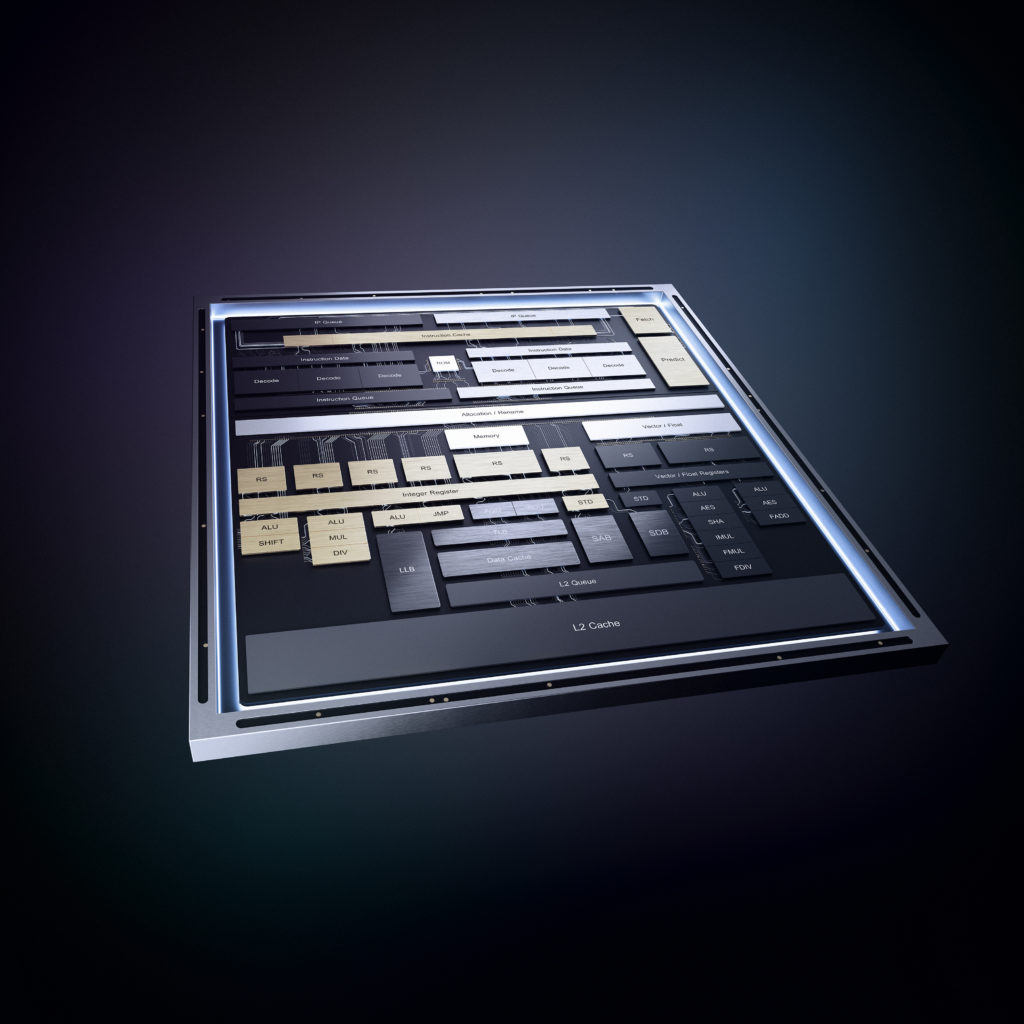

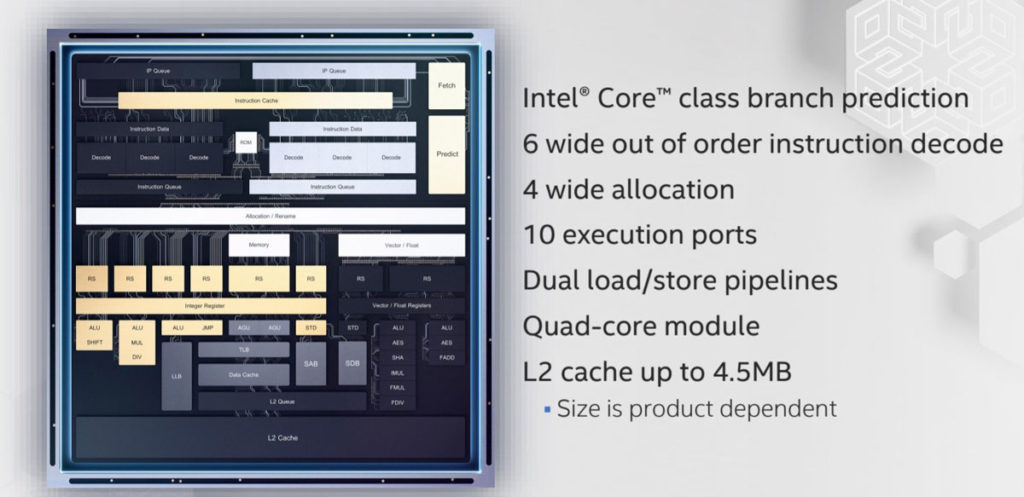

Intel Tremont has a core-class branch predictor with a 6-wide (2×3-wide clustered) out-of-order decoder in the front end for a more efficient feed to the wider back-end. This allows for an increase in performance while drawing on less power.

It also features four big allocations, ten back-end execution ports, and dual load/store pipelines. It also comes in a configuration of up to quad-cores with 4.5MB L2 cache capacity. Although, the size of the L2 cache varies depending on the component.

The low-power microarchitecture does deliver noticeable instructions-per-cycle (IPC) gains over Intel’s previous-generation low-power chips. The architecture also supports few technologies from Intel which include:

- Accelerator Interfacing Instructions

- Efficient and Scalable Work-Dispatch & Synchronization to Accelerators

- CPU Rooted Secure Boot

- Trusted Execution Technology

- Intel Boot Guard

- Intel Speed Shift

- Improved Responsiveness with Faster Hardware Controlled Frequency Changes

- Intel Total Memory Encryption

- Improve Confidentiality Protection in Memory from Physical Attacks.

However, even after all the above announcements, the company did not provide any release date. But since it’s been almost a year since Lakefield got introduced, we might not have to wait for much longer.

Do share your thoughts regarding the post in the comments section below. If you liked the content, please show your support by visiting and Following us on our Facebook and Twitter accounts.

Mobile Arrival Smartphones and gadget reviews, news and more.

Mobile Arrival Smartphones and gadget reviews, news and more.